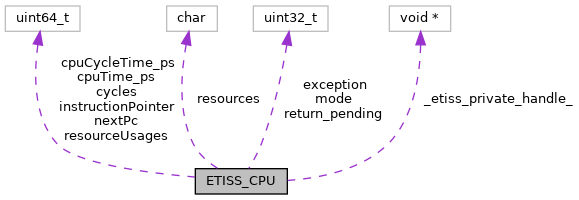

basic cpu state structure needed for execution of any cpu architecture. More...

#include <CPU.h>

Public Attributes | |

| etiss_uint64 | instructionPointer |

| pointer to next instruction. | |

| etiss_uint64 | nextPc |

| etiss_uint64 | cpuTime_ps |

| simulation time of cpu | |

| etiss_uint64 | resourceUsages [ETISS_MAX_RESOURCES] |

| how many cycles each resource is used | |

| const char * | resources [ETISS_MAX_RESOURCES] |

| names of resources | |

| etiss_uint64 | cycles [ETISS_MAX_RESOURCES] |

| how many cycles in each resource (including waiting) | |

| etiss_uint64 | cpuCycleTime_ps |

| frequency of the cpu. use to allign e.g. memory delays | |

| void * | _etiss_private_handle_ |

| private helper handle for plugins | |

| etiss_uint32 | mode |

| instruction set mode of the processor | |

| etiss_uint32 | exception |

| etiss_uint32 | return_pending |

Detailed Description

basic cpu state structure needed for execution of any cpu architecture.

to use this structure for an architecture it should be customized like this:

#pragma pack(push, 1) // important!

struct YOUR_CPU {

ETISS_CPU cpu;

etiss_uint32 your_registers[16];

[...]

};

#pragma pack(pop) // undo changes

now any pointer to YOUR_CPU can be directly casted to EITSS_CPU and back [YOUR_CPU ycpu; ETISS_CPU *

cpu = (ETISS_CPU *) &ycpu; YOUR_CPU * ycpuPtr = (YOUR_CPU *) cpu;] it is guaranteed that the cpu pointer passed

to generated code or functions of a CPUArch implementation was allocated by that CPUArch and can therefore be

casted without additional checks.

Member Data Documentation

◆ _etiss_private_handle_

| void * ETISS_CPU::_etiss_private_handle_ |

private helper handle for plugins

Definition at line 69 of file CPU.h.

Referenced by ETISS_SIGNAL_MMU(), etiss::CPUCore::execute(), etiss::CPUArchRegListenerInterface::signalChangedRegisterValue(), etiss::plugin::SelectiveSysWrapper::unwrap(), and etiss::plugin::SelectiveSysWrapper::wrap().

◆ cpuCycleTime_ps

| etiss_uint64 ETISS_CPU::cpuCycleTime_ps |

frequency of the cpu. use to allign e.g. memory delays

Definition at line 67 of file CPU.h.

Referenced by etiss_get_cycles(), etiss_get_instret(), etiss::CPUCore::execute(), RV32IMACFDArch::resetCPU(), and RV64IMACFDArch::resetCPU().

◆ cpuTime_ps

| etiss_uint64 ETISS_CPU::cpuTime_ps |

simulation time of cpu

Definition at line 59 of file CPU.h.

Referenced by etiss::plugin::InstructionAccurateCallback::call_on_entry(), etiss::plugin::fault::SwitchSystem::dread(), etiss::plugin::fault::SwitchSystem::dwrite(), etiss_get_cycles(), etiss_get_instret(), etiss::plugin::errorInjection::BlockAccurateHandler::execute(), etiss::InterruptHandler::execute(), etiss::CPUCore::execute(), etiss::plugin::fault::SwitchSystem::iread(), etiss::plugin::fault::SwitchSystem::iwrite(), etiss::interfaces::Delegate::read(), RV32IMACFDArch::resetCPU(), RV64IMACFDArch::resetCPU(), semihostingCall(), etiss::interfaces::Delegate::syncTime(), trace(), and etiss::interfaces::Delegate::write().

◆ cycles

| etiss_uint64 ETISS_CPU::cycles |

how many cycles in each resource (including waiting)

Definition at line 65 of file CPU.h.

Referenced by etiss::CPUCore::execute(), and handleResources().

◆ exception

| etiss_uint32 ETISS_CPU::exception |

Definition at line 73 of file CPU.h.

Referenced by etiss_icache_flush(), RV32IMACFD_raise(), RV64IMACFD_raise(), and semihostingCall().

◆ instructionPointer

| etiss_uint64 ETISS_CPU::instructionPointer |

pointer to next instruction.

NOTE: not neccessarily the instruction address (e.g instruction minimal size: 4; instruction pointer: 2 -> instruction address: 2*4)

Definition at line 54 of file CPU.h.

Referenced by access_error(), etiss::CPUCore::CPUCore(), TracePrinter::execute(), etiss::CPUCore::execute(), RV32IMACFDGDBCore::getInstructionPointer(), RV64IMACFDGDBCore::getInstructionPointer(), etiss::plugin::gdb::GDBCore::getInstructionPointer(), RV32IMACFDArch::handleException(), RV64IMACFDArch::handleException(), etiss::plugin::gdb::Server::postMemAccessCallback(), etiss::plugin::gdb::Server::preInstructionCallback(), RV32IMACFDArch::resetCPU(), RV64IMACFDArch::resetCPU(), RV32IMACFD_raise(), RV64IMACFD_raise(), trace(), and etiss::plugin::VariableValueLogger::writeValue().

◆ mode

| etiss_uint32 ETISS_CPU::mode |

instruction set mode of the processor

Definition at line 71 of file CPU.h.

Referenced by etiss::Translation::disasm(), etiss::Translation::getBlock(), RV32IMACFDArch::resetCPU(), RV64IMACFDArch::resetCPU(), and etiss::Translation::translateBlock().

◆ nextPc

| etiss_uint64 ETISS_CPU::nextPc |

Definition at line 57 of file CPU.h.

Referenced by RV32IMACFDArch::handleException(), RV64IMACFDArch::handleException(), RV32IMACFDArch::resetCPU(), and RV64IMACFDArch::resetCPU().

◆ resources

| const char * ETISS_CPU::resources |

◆ resourceUsages

| etiss_uint64 ETISS_CPU::resourceUsages |

how many cycles each resource is used

Definition at line 61 of file CPU.h.

Referenced by etiss::CPUCore::execute(), and handleResources().

◆ return_pending

| etiss_uint32 ETISS_CPU::return_pending |

Definition at line 74 of file CPU.h.

Referenced by RV32IMACFD_raise(), RV64IMACFD_raise(), and semihostingCall().

The documentation for this struct was generated from the following files: