#include <RV32IMACFDArch.h>

Public Member Functions | |

| RV32IMACFDArch (unsigned int) | |

| virtual const std::set< std::string > & | getListenerSupportedRegisters () |

| virtual ETISS_CPU * | newCPU () |

| allocate new cpu structure | |

| virtual void | resetCPU (ETISS_CPU *cpu, etiss::uint64 *startpointer) |

| reset cpu (structure) | |

| virtual void | deleteCPU (ETISS_CPU *) |

| delete cpu structure | |

| virtual std::shared_ptr< etiss::VirtualStruct > | getVirtualStruct (ETISS_CPU *cpu) |

| get the VirtualStruct of the core to mitigate register access | |

| virtual unsigned | getMaximumInstructionSizeInBytes () |

| virtual unsigned | getInstructionSizeInBytes () |

| virtual const std::set< std::string > & | getHeaders () const |

| required headers (RV32IMACFD.h) | |

| virtual etiss::int32 | handleException (etiss::int32 code, ETISS_CPU *cpu) |

| This function will be called automatically in order to handling architecure dependent exceptions such as interrupt, system call, illegal instructions. | |

| virtual void | initInstrSet (etiss::instr::ModedInstructionSet &) const |

| This function is called during CPUArch initialization. | |

| virtual void | initCodeBlock (etiss::CodeBlock &cb) const |

| called before instructions are translated for the code block | |

| virtual void | compensateEndianess (ETISS_CPU *cpu, etiss::instr::BitArray &ba) const |

| Target architecture may have inconsistent endianess. | |

| virtual etiss::InterruptVector * | createInterruptVector (ETISS_CPU *cpu) |

| If interrupt handling is expected, vector table could be provided to support interrupt triggering. | |

| virtual void | deleteInterruptVector (etiss::InterruptVector *vec, ETISS_CPU *cpu) |

| delete an allocated interrupt vector object | |

| virtual etiss::InterruptEnable * | createInterruptEnable (ETISS_CPU *cpu) |

| virtual void | deleteInterruptEnable (etiss::InterruptEnable *en, ETISS_CPU *cpu) |

| virtual etiss::plugin::gdb::GDBCore & | getGDBCore () |

| get the GDBcore for RV32IMACFD architecture | |

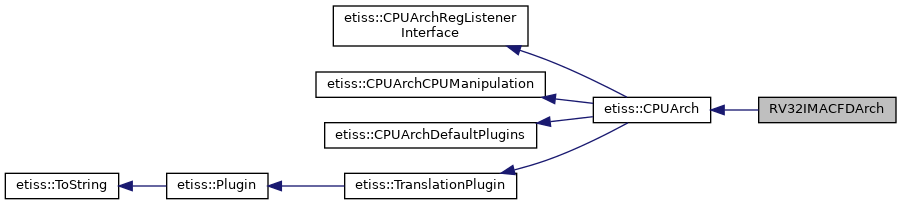

Public Member Functions inherited from etiss::CPUArch Public Member Functions inherited from etiss::CPUArch | |

| CPUArch (std::string archname) | |

| virtual | ~CPUArch () |

| std::string | getArchName () const |

| returns the name of this architecture. | |

| std::string | getName () const |

| returns the name of this architecture. | |

| virtual unsigned | getMaximumInstructionsPerMetaInstruction () |

| maximum number of instructions in a meta instruction | |

| virtual unsigned | getSuperInstructionCount () |

| fixed number of sub instructions per instruction (e.g. | |

| virtual std::string | getBlockGlobalCode () |

| get c++ code snippet that is placed at the top of a translated block | |

| virtual bool | unlikelyInstruction (etiss::uint8 *instr, unsigned length, bool &ismetainstruction) |

| return true if the given data is unlikely to be an instruction. | |

| virtual std::string | getIncludePath () |

| returns a path that will be used to look up header files | |

| virtual void | finalizeInstrSet (etiss::instr::ModedInstructionSet &) const |

| the default behavior of this function of a cpu arch is to add "cpu->cpuTime_ps += cpu->cpuCycleTime_ps;" if the cpu time update group is not in use | |

| virtual etiss::mm::MMU * | newMMU (ETISS_CPU *cpu) |

| It is an interface to instanciate a Memory Management Unit. | |

Public Member Functions inherited from etiss::CPUArchRegListenerInterface Public Member Functions inherited from etiss::CPUArchRegListenerInterface | |

| virtual | ~CPUArchRegListenerInterface () |

Public Member Functions inherited from etiss::CPUArchCPUManipulation Public Member Functions inherited from etiss::CPUArchCPUManipulation | |

| virtual | ~CPUArchCPUManipulation () |

Public Member Functions inherited from etiss::CPUArchDefaultPlugins Public Member Functions inherited from etiss::CPUArchDefaultPlugins | |

| virtual | ~CPUArchDefaultPlugins () |

| virtual etiss::Plugin * | newTimer (ETISS_CPU *cpu) |

| create a simple default timer implementaion instance for this architecture. | |

| virtual void | deleteTimer (etiss::Plugin *timer) |

| delete timer instance | |

Public Member Functions inherited from etiss::TranslationPlugin Public Member Functions inherited from etiss::TranslationPlugin | |

| TranslationPlugin () | |

| virtual | ~TranslationPlugin () |

| virtual void | finalizeCodeBlock (etiss::CodeBlock &) const |

| called after all instructions have been translated for the code block | |

| virtual void * | getPluginHandle () |

| called to get the handle that is available in translated code via getPoinerCode(). [default: this] | |

Public Member Functions inherited from etiss::Plugin Public Member Functions inherited from etiss::Plugin | |

| virtual | ~Plugin () |

| unsigned | getType () |

| InterruptListenerPlugin * | getInterruptListenerPlugin () |

| CoroutinePlugin * | getCoroutinePlugin () |

| SystemWrapperPlugin * | getSystemWrapperPlugin () |

| RegisterDevicePlugin * | getRegisterDevicePlugin () |

| TranslationPlugin * | getTranslationPlugin () |

| std::string | getPluginName () const |

| const std::string & | getLastAssignedCoreName () |

| std::string | toString () const |

Public Member Functions inherited from etiss::ToString Public Member Functions inherited from etiss::ToString | |

| ToString () | |

| virtual | ~ToString () |

Private Attributes | |

| std::set< std::string > | listenerSupportedRegisters_ |

| std::set< std::string > | headers_ |

| RV32IMACFDGDBCore | gdbcore_ |

| unsigned int | coreno_ |

Additional Inherited Members | |

Static Public Member Functions inherited from etiss::CPUArchRegListenerInterface Static Public Member Functions inherited from etiss::CPUArchRegListenerInterface | |

| static void | signalChangedRegisterValue (ETISS_CPU *cpu, const char *registerName) |

| call this function to inform RegisterDevicePlugins about changed special register values. | |

Static Public Attributes inherited from etiss::Plugin Static Public Attributes inherited from etiss::Plugin | |

| static const unsigned | INTERRUPTLISTENER = 1 << 0 |

| access to translated code | |

| static const unsigned | COROUTINE = 1 << 1 |

| callback after execution of each translated block | |

| static const unsigned | SYSTEMWRAPPER = 1 << 2 |

| can wrap/change ETISS_System structure at execution start | |

| static const unsigned | REGISTERDEVICE |

| gets noticed of changes to special registers (e.g. mmu register etc. [depends on architecture]) | |

| static const unsigned | TRANSLATION |

| access to translated code during translation phase or when instruction tree is built | |

Protected Member Functions inherited from etiss::CPUArch Protected Member Functions inherited from etiss::CPUArch | |

| virtual std::string | _getPluginName () const |

| do not override. maps to getName(). | |

Protected Member Functions inherited from etiss::TranslationPlugin Protected Member Functions inherited from etiss::TranslationPlugin | |

| std::string | getPointerCode () const |

| returns a C code expression that allows to get or assign a pointer to the variable assigned to this translation plugin. | |

Protected Member Functions inherited from etiss::Plugin Protected Member Functions inherited from etiss::Plugin | |

| Plugin (unsigned type=0) | |

| virtual void | init (ETISS_CPU *cpu, ETISS_System *system, CPUArch *arch) |

| this function is called before the plugin is used in the cpu execution loop (etiss::CPUCore::execute). | |

| virtual void | cleanup () |

| this function is called after cpu execution loop (etiss::CPUCore::execute) finished. | |

| void | setCorrespondingCPUCoreName (std::string name) |

| virtual void | addedToCPUCore (etiss::CPUCore *core) |

| called as soon a plugin has been added to its CPUCore. | |

| virtual void | removedFromCPUCore (etiss::CPUCore *core) |

| called as soon a plugin has been removed from its CPUCore. | |

Protected Attributes inherited from etiss::Plugin Protected Attributes inherited from etiss::Plugin | |

| ETISS_CPU * | plugin_cpu_ |

| holds a pointer to the cpu structure. will be set before init call and after cleanup call | |

| ETISS_System * | plugin_system_ |

| holds a pointer to the system structure. | |

| CPUArch * | plugin_arch_ |

| holds a pointer to the CPUArch instance. will be set before init call and after cleanup call | |

| CPUCore * | plugin_core_ |

| holds a pointer to the associated CPUCore instance. | |

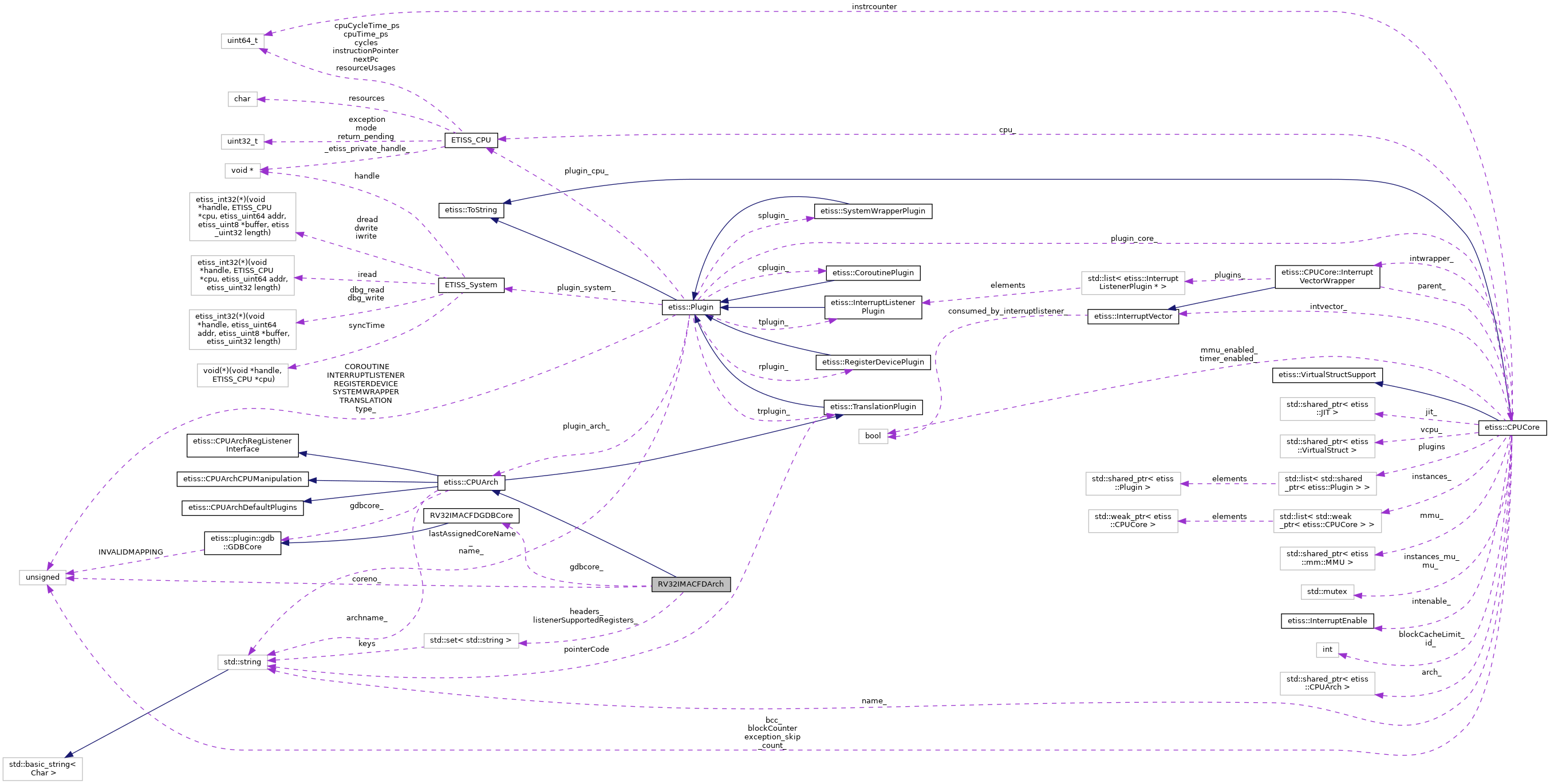

Detailed Description

Definition at line 28 of file RV32IMACFDArch.h.

Constructor & Destructor Documentation

◆ RV32IMACFDArch()

| RV32IMACFDArch::RV32IMACFDArch | ( | unsigned int | coreno | ) |

Definition at line 44 of file RV32IMACFDArch.cpp.

References headers_.

Member Function Documentation

◆ compensateEndianess()

|

virtual |

Target architecture may have inconsistent endianess.

This function is called whenever a data is read from memory.

Data read from memory is buffered, and this function is called to alter sequence of buffered data so that the inconsistent endianess is compensated.

- See also

- RV32IMACFDArchSpecificImp.h

Target architecture may have inconsistent endianess. Data read from memory is buffered, and this function is called to alter sequence of buffered data so that the inconsistent endianess is compensated.

Example for ARMv6M: ``` void * ptr = ba.internalBuffer(); if (ba.byteCount() == 2) { *((uint32_t*)ptr) = ((uint16_t)(*((uint8_t*)ptr))) | ((uint16_t)(*(((uint8_t*)ptr)+1)) << 8); } else if (ba.byteCount() == 4) { *((uint32_t*)ptr) = ((((uint32_t)(*((uint8_t*)ptr))) | ((uint32_t)(*(((uint8_t*)ptr)+1)) << 8)) << 16) | ((uint32_t)(*(((uint8_t*)ptr)+2)) ) | ((uint32_t)(*(((uint8_t*)ptr)+3)) << 8); } else { etiss::log(etiss::FATALERROR,"Endianess cannot be handled",ba.byteCount()); } ```

- Attention

- Default endianess: little-endian

Reimplemented from etiss::CPUArch.

Definition at line 320 of file RV32IMACFDArchSpecificImp.cpp.

◆ createInterruptEnable()

|

virtual |

Reimplemented from etiss::CPUArch.

Definition at line 365 of file RV32IMACFDArchSpecificImp.cpp.

◆ createInterruptVector()

|

virtual |

If interrupt handling is expected, vector table could be provided to support interrupt triggering.

- See also

- RV32IMACFDArchSpecificImp.h

Interrupt vector table is used to inform the core whenever an edge/level triggered interrupt incoming. The content of interrupt vector could be a special register or standalone interrupt lines.

Reimplemented from etiss::CPUArch.

Definition at line 346 of file RV32IMACFDArchSpecificImp.cpp.

◆ deleteCPU()

|

virtual |

◆ deleteInterruptEnable()

|

virtual |

Reimplemented from etiss::CPUArch.

Definition at line 370 of file RV32IMACFDArchSpecificImp.cpp.

◆ deleteInterruptVector()

|

virtual |

delete an allocated interrupt vector object

Reimplemented from etiss::CPUArch.

Definition at line 360 of file RV32IMACFDArchSpecificImp.cpp.

◆ getGDBCore()

|

virtual |

get the GDBcore for RV32IMACFD architecture

- See also

- RV32IMACFDGDBCore.h for implementation of GDBcore

Reimplemented from etiss::CPUArch.

Definition at line 226 of file RV32IMACFDArch.cpp.

References gdbcore_.

◆ getHeaders()

|

virtual |

required headers (RV32IMACFD.h)

Implements etiss::CPUArch.

Definition at line 212 of file RV32IMACFDArch.cpp.

References headers_.

◆ getInstructionSizeInBytes()

|

virtual |

◆ getListenerSupportedRegisters()

|

virtual |

- See also

- CPUArchRegListenerInterface::signalChangedRegisterValue

Implements etiss::CPUArchRegListenerInterface.

Definition at line 49 of file RV32IMACFDArch.cpp.

References listenerSupportedRegisters_.

◆ getMaximumInstructionSizeInBytes()

|

virtual |

- Returns

- 8 (jump instruction + instruction of delay slot)

Implements etiss::CPUArch.

Definition at line 196 of file RV32IMACFDArch.cpp.

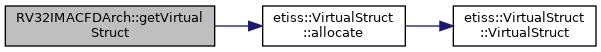

◆ getVirtualStruct()

|

virtual |

get the VirtualStruct of the core to mitigate register access

- See also

- RV32IMACFDArchSpecificImp.h

Implements etiss::CPUArchCPUManipulation.

Definition at line 327 of file RV32IMACFDArchSpecificImp.cpp.

References etiss::VirtualStruct::allocate(), and uint32_t.

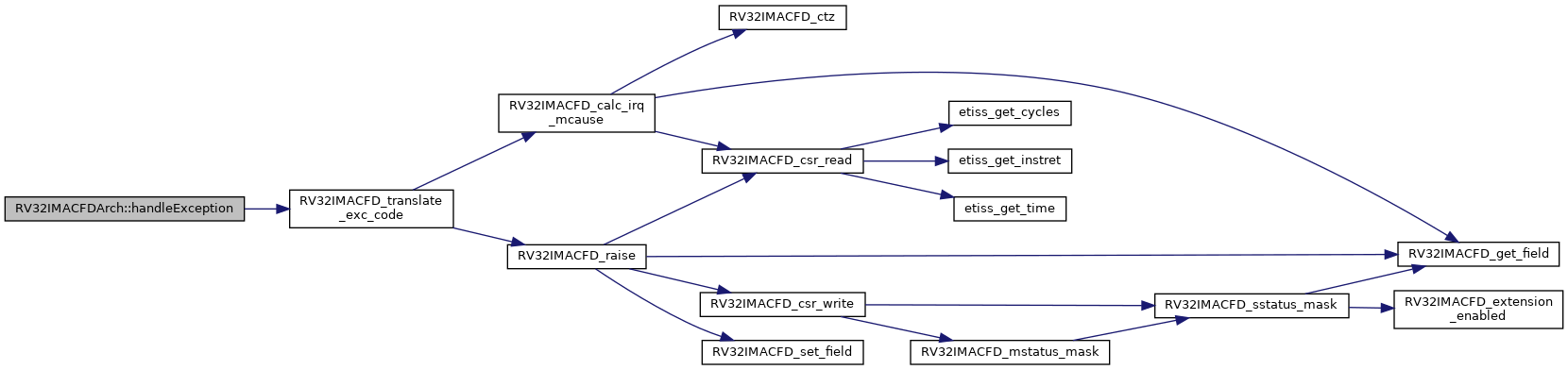

◆ handleException()

|

virtual |

This function will be called automatically in order to handling architecure dependent exceptions such as interrupt, system call, illegal instructions.

Generated on Thu, 24 Feb 2022 17:15:20 +0100.

- See also

- RV32IMACFDArchSpecificImp.h

This file contains the architecture specific implementation for the RV32IMACFD core architecture.

WARNING: This file contains user-added code, be mindful when overwriting this with generated code!

This function will be called automatically in order to handling exceptions such as interrupt, system call, illegal instructions

Exception handling mechanism is implementation dependent for each cpu variant. Please add it to the following block if exception handling is demanded. Pseudo example: ``` switch(cause) { case etiss::RETURNCODE::INTERRUPT: break; } ```

Reimplemented from etiss::CPUArch.

Definition at line 35 of file RV32IMACFDArchSpecificImp.cpp.

References ETISS_CPU::instructionPointer, ETISS_CPU::nextPc, and RV32IMACFD_translate_exc_code().

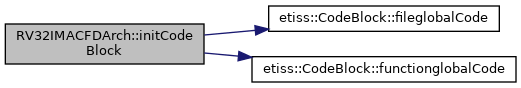

◆ initCodeBlock()

|

virtual |

called before instructions are translated for the code block

Reimplemented from etiss::TranslationPlugin.

Definition at line 217 of file RV32IMACFDArch.cpp.

References etiss::CodeBlock::fileglobalCode(), and etiss::CodeBlock::functionglobalCode().

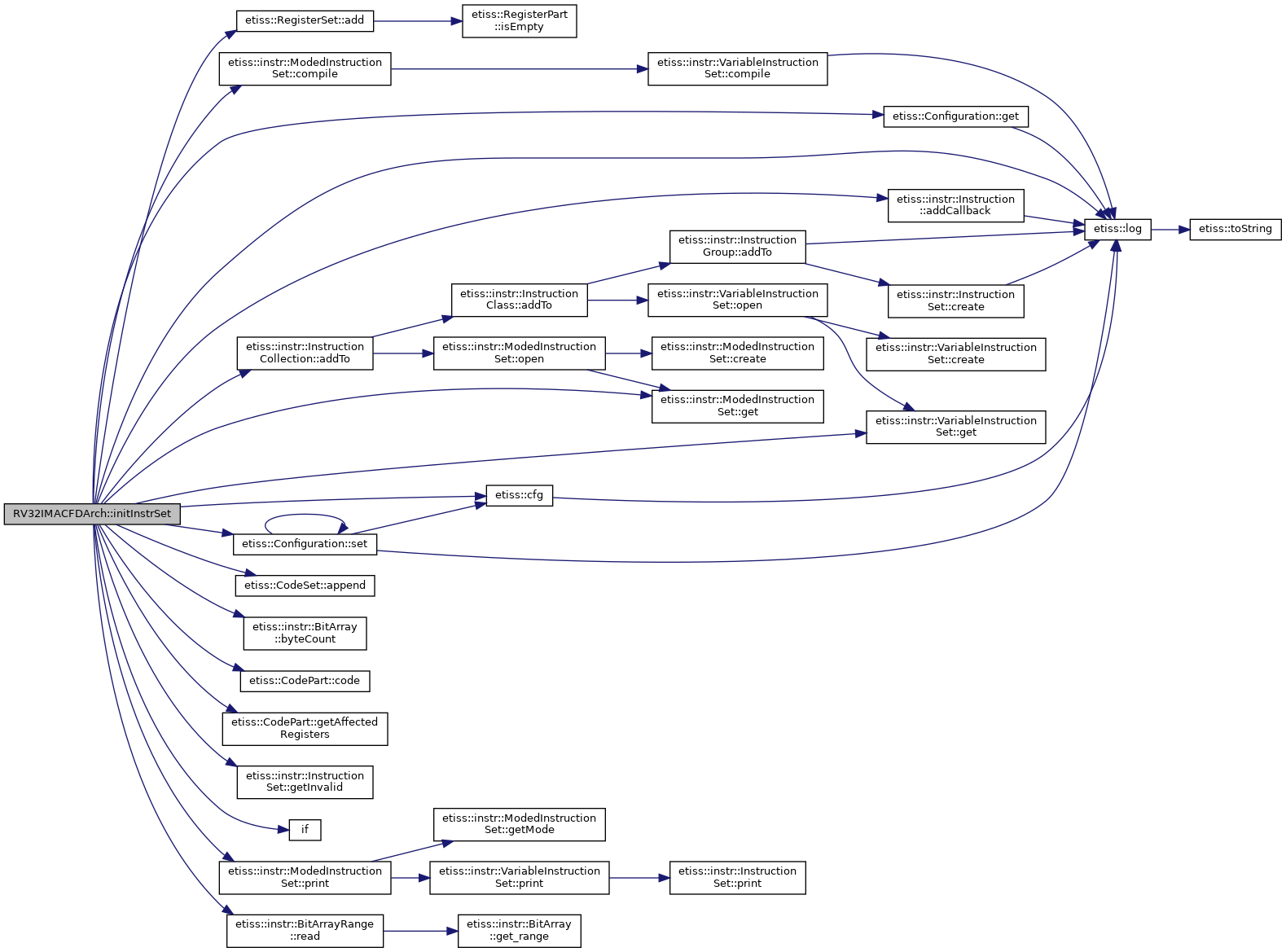

◆ initInstrSet()

|

virtual |

This function is called during CPUArch initialization.

- See also

- RV32IMACFDArchSpecificImp.h

Function pointer length_updater_ has to be replaced if multiple length instruction execution is supported. This function enables dynamic instruction length update in order to guarantee correct binary translation Pseudo example: ``` vis->length_updater_ = [](VariableInstructionSet & ,InstructionContext & ic, BitArray & { switch(ba.byteCount()) { case 4: if ( INSTRUCTION_LENTH_NOT_EQUAL(4)) { updateInstrLength(ic, ba); ic.is_not_default_width_ = true; } break; } }; ```

Reimplemented from etiss::TranslationPlugin.

Definition at line 66 of file RV32IMACFDArchSpecificImp.cpp.

References etiss::RegisterSet::add(), etiss::instr::Instruction::addCallback(), etiss::instr::InstructionCollection::addTo(), etiss::CodeSet::append(), etiss::instr::BitArray::byteCount(), etiss::cfg(), etiss::CodePart::code(), etiss::instr::ModedInstructionSet::compile(), etiss::instr::InstructionContext::current_address_, etiss::FATALERROR, etiss::Configuration::get(), etiss::instr::ModedInstructionSet::get(), etiss::instr::VariableInstructionSet::get(), etiss::CodePart::getAffectedRegisters(), etiss::instr::InstructionSet::getInvalid(), etiss::instr::InstructionContext::instr_width_, etiss::instr::InstructionContext::instr_width_fully_evaluated_, etiss::instr::InstructionContext::is_not_default_width_, etiss::instr::VariableInstructionSet::length_updater_, etiss::log(), etiss::instr::ModedInstructionSet::print(), etiss::instr::BitArrayRange::read(), RV32IMACFDISA, and etiss::Configuration::set().

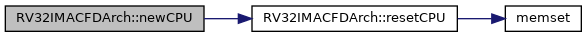

◆ newCPU()

|

virtual |

allocate new cpu structure

Implements etiss::CPUArch.

Definition at line 54 of file RV32IMACFDArch.cpp.

References resetCPU().

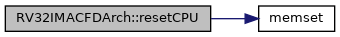

◆ resetCPU()

|

virtual |

reset cpu (structure)

Implements etiss::CPUArch.

Definition at line 61 of file RV32IMACFDArch.cpp.

References RV32IMACFD::A0, RV32IMACFD::A1, RV32IMACFD::A2, RV32IMACFD::A3, RV32IMACFD::A4, RV32IMACFD::A5, RV32IMACFD::A6, RV32IMACFD::A7, ETISS_CPU::cpuCycleTime_ps, ETISS_CPU::cpuTime_ps, RV32IMACFD::CSR, RV32IMACFD::DPC, RV32IMACFD::F, RV32IMACFD::FCSR, RV32IMACFD::FENCE, RV32IMACFD::GP, RV32IMACFD::ins_CSR, RV32IMACFD::ins_X, ETISS_CPU::instructionPointer, memset(), RV32IMACFD::MIE, RV32IMACFD::MIP, ETISS_CPU::mode, RV32IMACFD::MSTATUS, ETISS_CPU::nextPc, RV32IMACFD::PRIV, RV32IMACFD::RA, RV32IMACFD::RES, RV32IMACFD::RES_ADDR, RV32IMACFD::S0, RV32IMACFD::S1, RV32IMACFD::S10, RV32IMACFD::S11, RV32IMACFD::S2, RV32IMACFD::S3, RV32IMACFD::S4, RV32IMACFD::S5, RV32IMACFD::S6, RV32IMACFD::S7, RV32IMACFD::S8, RV32IMACFD::S9, RV32IMACFD::SP, RV32IMACFD::T0, RV32IMACFD::T1, RV32IMACFD::T2, RV32IMACFD::T3, RV32IMACFD::T4, RV32IMACFD::T5, RV32IMACFD::T6, RV32IMACFD::TP, RV32IMACFD::X, and RV32IMACFD::ZERO.

Referenced by newCPU().

Member Data Documentation

◆ coreno_

|

private |

Definition at line 107 of file RV32IMACFDArch.h.

◆ gdbcore_

|

private |

Definition at line 106 of file RV32IMACFDArch.h.

Referenced by getGDBCore().

◆ headers_

|

private |

Definition at line 105 of file RV32IMACFDArch.h.

Referenced by getHeaders(), and RV32IMACFDArch().

◆ listenerSupportedRegisters_

|

private |

Definition at line 104 of file RV32IMACFDArch.h.

Referenced by getListenerSupportedRegisters().

The documentation for this class was generated from the following files:

- /home/runner/work/etiss/etiss/ArchImpl/RV32IMACFD/RV32IMACFDArch.h

- /home/runner/work/etiss/etiss/ArchImpl/RV32IMACFD/RV32IMACFDArch.cpp

- /home/runner/work/etiss/etiss/ArchImpl/RV32IMACFD/RV32IMACFDArchSpecificImp.cpp