#include <MMU.h>

Public Member Functions | |

| MMU (bool hw_ptw, std::string name, bool pid_enabled) | |

| MMU ctor. | |

| virtual | ~MMU () |

| virtual int32_t | Translate (const uint64_t vma, uint64_t *const pma_buf, MM_ACCESS access, uint64_t data=0) |

| Conduct the actual translation according to the format set by PTEFormatBuilder. | |

| void | SignalMMU (uint64_t control_reg_val_) |

| Whenever the MMU control register changes, the MMU has to be notified with the updated control register value. | |

| void | Dump () |

| Dump the details of the MMU, when page fault cannot be handled. | |

| void | Init (ETISS_CPU *cpu, ETISS_System *system) |

| Initialize the MMU, when DMMUWrapper is wrapping the MMU. | |

| void | AddTLBEntryMap (uint64_t phy_addr_, PTE &pte) |

| Keep a record of mapping between cached PTE with its physical address. | |

| virtual bool | CheckPrivilegedMode ()=0 |

| MMU is enabled in certain mode. | |

| virtual int32_t | CheckProtection (const PTE &, MM_ACCESS access)=0 |

| Memory protection is architecture-dependent, which should be implemented with architecture model. | |

| virtual int32_t | WalkPageTable (uint64_t, MM_ACCESS) |

| Page table walking is required to translate virtual address to physical address if TLB miss occurs. | |

| virtual void | UpdatePTEFlags (PTE &, MM_ACCESS) |

| Reserved for some MMU that might update PTE when translating. | |

| bool | IsTLBFull () const |

| PTE | EvictTLBEntry (const uint64_t vfn) |

| bool | HasPageTableWalker () |

| bool | IsProcessIdEnabled () |

| void | UpdatePid (uint32_t new_pid) |

| uint64_t | GetMMUControlReg () |

| int32_t | AddTLBEntry (const uint64_t vfn, const PTE &pte) |

| std::string | GetName () const |

| virtual int32_t | GetPid (uint64_t control_reg_val_) |

Public Attributes | |

| bool | cache_flush_pending |

Protected Attributes | |

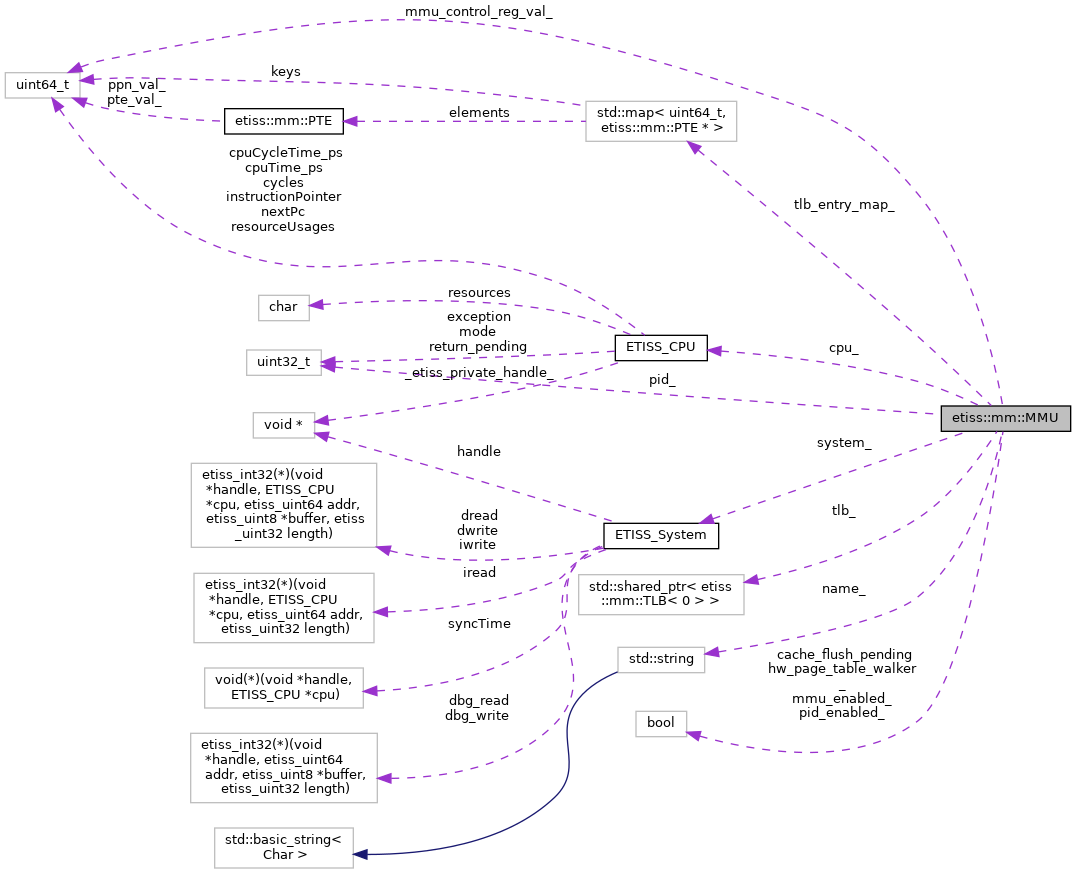

| ETISS_CPU * | cpu_ |

| ETISS_System * | system_ |

| bool | mmu_enabled_ |

Private Attributes | |

| std::shared_ptr< etiss::mm::TLB< 0 > > | tlb_ |

| std::map< uint64_t, PTE * > | tlb_entry_map_ |

| uint64_t | mmu_control_reg_val_ |

| uint32_t | pid_ |

| std::string | name_ |

| const bool | pid_enabled_ |

| const bool | hw_page_table_walker_ |

Detailed Description

Constructor & Destructor Documentation

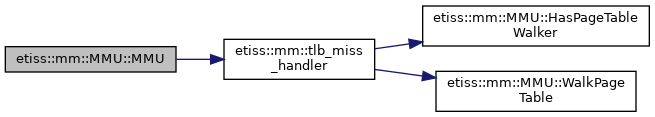

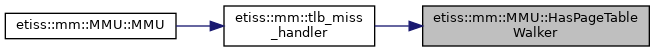

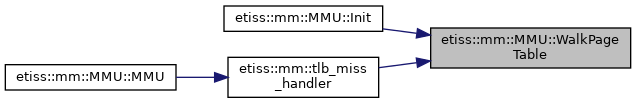

◆ MMU()

MMU ctor.

It is needed to explicitly declared whether the MMU has a hardware page table walker, or support process identifier

Definition at line 30 of file MMU.cpp.

References REGISTER_PAGE_FAULT_HANDLER, tlb_, etiss::mm::tlb_miss_handler(), and etiss::mm::TLBMISS.

◆ ~MMU()

Member Function Documentation

◆ AddTLBEntry()

Definition at line 119 of file MMU.cpp.

References HANDLE_PAGE_FAULT, int32_t, etiss::mm::NOERROR, etiss::mm::R_ACCESS, tlb_, and uint32_t.

◆ AddTLBEntryMap()

Keep a record of mapping between cached PTE with its physical address.

Definition at line 179 of file MMU.cpp.

References HANDLE_PAGE_FAULT, etiss::mm::PTEOVERLAP, etiss::mm::R_ACCESS, and tlb_entry_map_.

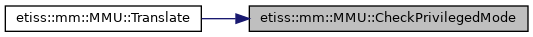

◆ CheckPrivilegedMode()

|

pure virtual |

MMU is enabled in certain mode.

Thus the privilege mode check should be implemented in architectural part

Referenced by Translate().

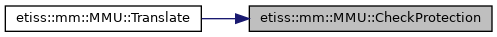

◆ CheckProtection()

Memory protection is architecture-dependent, which should be implemented with architecture model.

Referenced by Translate().

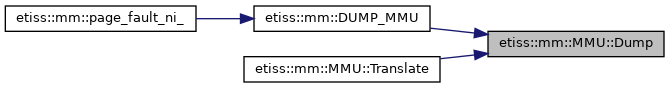

◆ Dump()

| void etiss::mm::MMU::Dump | ( | ) |

Dump the details of the MMU, when page fault cannot be handled.

Definition at line 154 of file MMU.cpp.

References mmu_control_reg_val_, mmu_enabled_, name_, pid_, pid_enabled_, and tlb_.

Referenced by etiss::mm::DUMP_MMU(), and Translate().

◆ EvictTLBEntry()

◆ GetMMUControlReg()

|

inline |

Definition at line 131 of file MMU.h.

References mmu_control_reg_val_.

◆ GetName()

|

inline |

Definition at line 135 of file MMU.h.

References name_.

Referenced by SignalMMU().

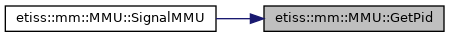

◆ GetPid()

Definition at line 137 of file MMU.h.

Referenced by SignalMMU().

◆ HasPageTableWalker()

|

inline |

Definition at line 121 of file MMU.h.

References hw_page_table_walker_.

Referenced by etiss::mm::tlb_miss_handler().

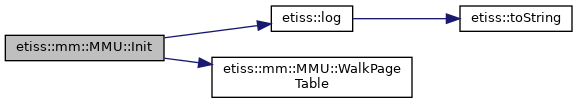

◆ Init()

| void etiss::mm::MMU::Init | ( | ETISS_CPU * | cpu, |

| ETISS_System * | system | ||

| ) |

Initialize the MMU, when DMMUWrapper is wrapping the MMU.

- See also

- etiss::mm::DMMUWrapper

Definition at line 169 of file MMU.cpp.

References cpu_, DEFAULT_PAGE_TABLE_WALKER, etiss::FATALERROR, hw_page_table_walker_, etiss::log(), etiss::mm::R_ACCESS, system_, and WalkPageTable().

◆ IsProcessIdEnabled()

|

inline |

Definition at line 123 of file MMU.h.

References pid_enabled_.

◆ IsTLBFull()

|

inline |

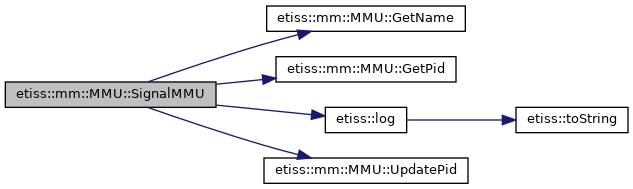

◆ SignalMMU()

| void etiss::mm::MMU::SignalMMU | ( | uint64_t | control_reg_val_ | ) |

Whenever the MMU control register changes, the MMU has to be notified with the updated control register value.

Definition at line 131 of file MMU.cpp.

References cache_flush_pending, GetName(), GetPid(), etiss::log(), mmu_control_reg_val_, mmu_enabled_, pid_enabled_, tlb_, tlb_entry_map_, UpdatePid(), etiss::VERBOSE, and etiss::WARNING.

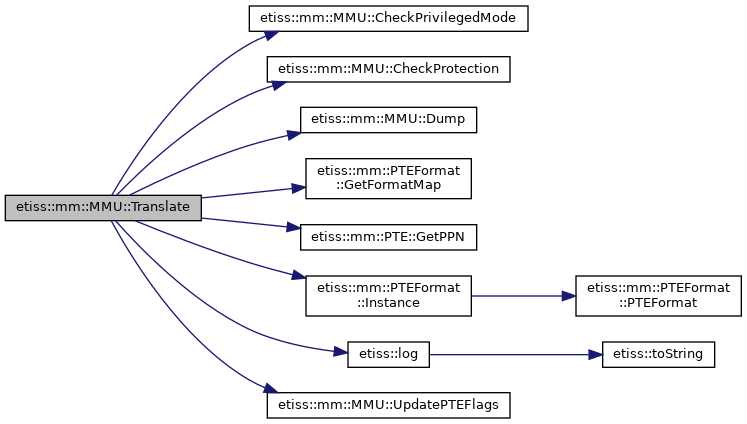

◆ Translate()

|

virtual |

Conduct the actual translation according to the format set by PTEFormatBuilder.

Definition at line 44 of file MMU.cpp.

References CheckPrivilegedMode(), CheckProtection(), Dump(), etiss::FATALERROR, etiss::mm::PTEFormat::GetFormatMap(), etiss::mm::PTE::GetPPN(), HANDLE_PAGE_FAULT, etiss::mm::PTEFormat::Instance(), int32_t, etiss::log(), mmu_enabled_, etiss::mm::NOERROR, pid_, pid_enabled_, tlb_, tlb_entry_map_, uint32_t, uint64_t, UpdatePTEFlags(), and etiss::mm::W_ACCESS.

◆ UpdatePid()

|

inline |

Definition at line 125 of file MMU.h.

References pid_, and pid_enabled_.

Referenced by SignalMMU().

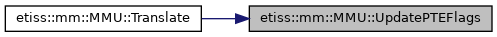

◆ UpdatePTEFlags()

Reserved for some MMU that might update PTE when translating.

Definition at line 115 of file MMU.h.

Referenced by Translate().

◆ WalkPageTable()

Page table walking is required to translate virtual address to physical address if TLB miss occurs.

Definition at line 109 of file MMU.h.

References DEFAULT_PAGE_TABLE_WALKER.

Referenced by Init(), and etiss::mm::tlb_miss_handler().

Member Data Documentation

◆ cache_flush_pending

| bool etiss::mm::MMU::cache_flush_pending |

Definition at line 139 of file MMU.h.

Referenced by SignalMMU().

◆ cpu_

|

protected |

◆ hw_page_table_walker_

|

private |

Definition at line 160 of file MMU.h.

Referenced by HasPageTableWalker(), and Init().

◆ mmu_control_reg_val_

|

private |

Definition at line 155 of file MMU.h.

Referenced by Dump(), GetMMUControlReg(), and SignalMMU().

◆ mmu_enabled_

|

protected |

Definition at line 144 of file MMU.h.

Referenced by Dump(), SignalMMU(), and Translate().

◆ name_

|

private |

◆ pid_

|

private |

Definition at line 156 of file MMU.h.

Referenced by Dump(), Translate(), and UpdatePid().

◆ pid_enabled_

|

private |

Definition at line 159 of file MMU.h.

Referenced by Dump(), IsProcessIdEnabled(), SignalMMU(), Translate(), and UpdatePid().

◆ system_

|

protected |

◆ tlb_

|

private |

Definition at line 148 of file MMU.h.

Referenced by AddTLBEntry(), Dump(), EvictTLBEntry(), IsTLBFull(), MMU(), SignalMMU(), and Translate().

◆ tlb_entry_map_

Definition at line 153 of file MMU.h.

Referenced by AddTLBEntryMap(), SignalMMU(), and Translate().

The documentation for this class was generated from the following files: