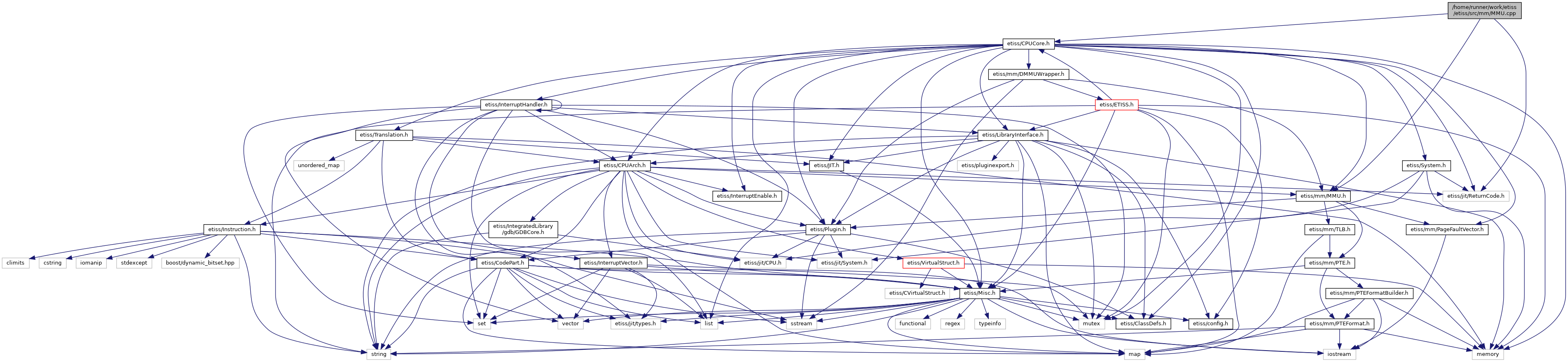

Modeling hardware memory management for virtual memory -> physical memory translation and protection. More...

Go to the source code of this file.

Namespaces | |

| namespace | etiss |

| forwards: include/jit/* | |

| namespace | etiss::mm |

Functions | |

| int32_t | etiss::mm::tlb_miss_handler (int32_t fault, MMU *mmu, uint64_t vma, MM_ACCESS access) |

| void | etiss::mm::DUMP_MMU (MMU *mmu) |

| void | ETISS_SIGNAL_MMU (ETISS_CPU *cpu, etiss_uint64 mmu_signal_) |

Detailed Description

Modeling hardware memory management for virtual memory -> physical memory translation and protection.

It is oriented for porting OS to ETISS.

Memory Management Unit is the key component to support OS. Modern architectures vote for TLB to speed up virtual memory address (vma) to physical memory address (pma) translation. Since vma to pma could easily become the bottleneck, it is assumed hardware managed TLB is adopted. As for software managed TLB (old design), MMU has to be modified accordingly.

Definition in file MMU.cpp.

Function Documentation

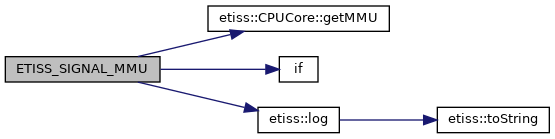

◆ ETISS_SIGNAL_MMU()

| void ETISS_SIGNAL_MMU | ( | ETISS_CPU * | cpu, |

| etiss_uint64 | mmu_signal_ | ||

| ) |

Definition at line 221 of file MMU.cpp.

References ETISS_CPU::_etiss_private_handle_, etiss::ERROR, etiss::CPUCore::getMMU(), and etiss::log().