contains neccesary interfaces for instruction translation. More...

#include <map>#include <set>#include <string>#include "etiss/Misc.h"#include "etiss/IntegratedLibrary/gdb/GDBCore.h"#include "etiss/Plugin.h"

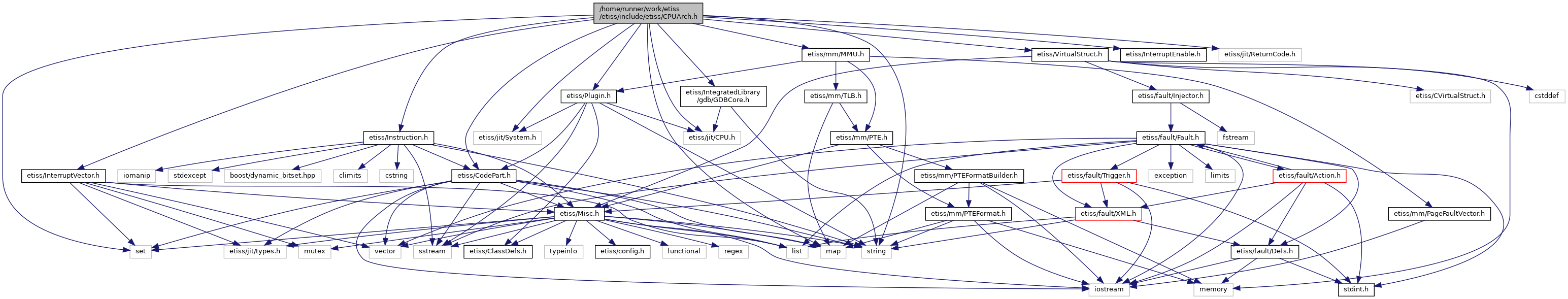

Include dependency graph for CPUArch.h:

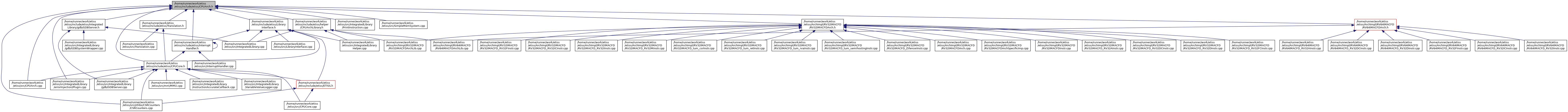

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| class | etiss::CPUArchRegListenerInterface |

| allows to inform plugins about changes to a register that is present in the cpu structure. More... | |

| class | etiss::CPUArchCPUManipulation |

| interface for cpu structure access. More... | |

| class | etiss::CPUArchDefaultPlugins |

| provides common basic plugins More... | |

| class | etiss::CPUArch |

| the interface to translate instructions of and processor architecture More... | |

Namespaces | |

| namespace | etiss |

| forwards: include/jit/* | |

Detailed Description

contains neccesary interfaces for instruction translation.

to enable ETISS to translate instructions of a certain ISA the etiss::CPUArch class needs to be extended/implemented. etiss::CPUArch inherits all other classes defined in this header file. Those classes are intended to provide structuring of member functions by purpose.

Definition in file CPUArch.h.