Generated on Mon, 27 Apr 2026 10:48:13 +0000. More...

#include <RV64IMACFD.h>

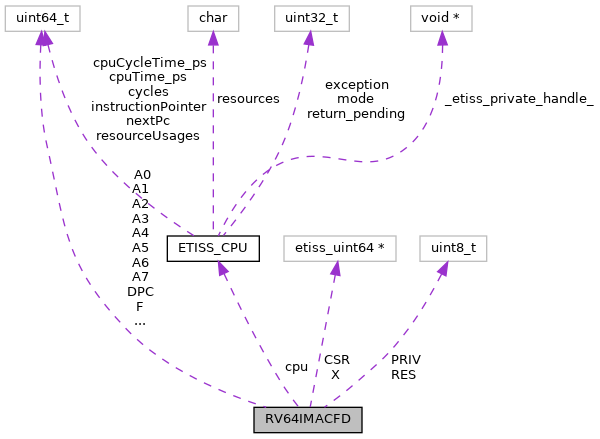

Detailed Description

Generated on Mon, 27 Apr 2026 10:48:13 +0000.

This file contains the registers for the RV64IMACFD core architecture.

Definition at line 17 of file RV64IMACFD.h.

Member Data Documentation

◆ A0

| etiss_uint64 RV64IMACFD::A0 |

Definition at line 31 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ A1

| etiss_uint64 RV64IMACFD::A1 |

Definition at line 32 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ A2

| etiss_uint64 RV64IMACFD::A2 |

Definition at line 33 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ A3

| etiss_uint64 RV64IMACFD::A3 |

Definition at line 34 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ A4

| etiss_uint64 RV64IMACFD::A4 |

Definition at line 35 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ A5

| etiss_uint64 RV64IMACFD::A5 |

Definition at line 36 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ A6

| etiss_uint64 RV64IMACFD::A6 |

Definition at line 37 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ A7

| etiss_uint64 RV64IMACFD::A7 |

Definition at line 38 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ cpu

| ETISS_CPU RV64IMACFD::cpu |

Definition at line 19 of file RV64IMACFD.h.

◆ CSR

| etiss_uint64 * RV64IMACFD::CSR |

Definition at line 63 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ DPC

| etiss_uint64 RV64IMACFD::DPC |

Definition at line 58 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ F

| etiss_uint64 RV64IMACFD::F |

Definition at line 65 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ FCSR

| etiss_uint64 RV64IMACFD::FCSR |

Definition at line 59 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ FENCE

| etiss_uint64 RV64IMACFD::FENCE |

Definition at line 55 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ GP

| etiss_uint64 RV64IMACFD::GP |

Definition at line 24 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ ins_CSR

| etiss_uint64 RV64IMACFD::ins_CSR |

Definition at line 64 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ ins_X

| etiss_uint64 RV64IMACFD::ins_X |

Definition at line 54 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ MIE

| etiss_uint64 RV64IMACFD::MIE |

Definition at line 61 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ MIP

| etiss_uint64 RV64IMACFD::MIP |

Definition at line 62 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ MSTATUS

| etiss_uint64 RV64IMACFD::MSTATUS |

Definition at line 60 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ PRIV

| etiss_uint8 RV64IMACFD::PRIV |

Definition at line 57 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ RA

| etiss_uint64 RV64IMACFD::RA |

Definition at line 22 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ RES

| etiss_uint8 RV64IMACFD::RES |

Definition at line 56 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ RES_ADDR

| etiss_uint64 RV64IMACFD::RES_ADDR |

Definition at line 66 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ S0

| etiss_uint64 RV64IMACFD::S0 |

Definition at line 29 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ S1

| etiss_uint64 RV64IMACFD::S1 |

Definition at line 30 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ S10

| etiss_uint64 RV64IMACFD::S10 |

Definition at line 47 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ S11

| etiss_uint64 RV64IMACFD::S11 |

Definition at line 48 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ S2

| etiss_uint64 RV64IMACFD::S2 |

Definition at line 39 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ S3

| etiss_uint64 RV64IMACFD::S3 |

Definition at line 40 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ S4

| etiss_uint64 RV64IMACFD::S4 |

Definition at line 41 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ S5

| etiss_uint64 RV64IMACFD::S5 |

Definition at line 42 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ S6

| etiss_uint64 RV64IMACFD::S6 |

Definition at line 43 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ S7

| etiss_uint64 RV64IMACFD::S7 |

Definition at line 44 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ S8

| etiss_uint64 RV64IMACFD::S8 |

Definition at line 45 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ S9

| etiss_uint64 RV64IMACFD::S9 |

Definition at line 46 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ SP

| etiss_uint64 RV64IMACFD::SP |

Definition at line 23 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ T0

| etiss_uint64 RV64IMACFD::T0 |

Definition at line 26 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ T1

| etiss_uint64 RV64IMACFD::T1 |

Definition at line 27 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ T2

| etiss_uint64 RV64IMACFD::T2 |

Definition at line 28 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ T3

| etiss_uint64 RV64IMACFD::T3 |

Definition at line 49 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ T4

| etiss_uint64 RV64IMACFD::T4 |

Definition at line 50 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ T5

| etiss_uint64 RV64IMACFD::T5 |

Definition at line 51 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ T6

| etiss_uint64 RV64IMACFD::T6 |

Definition at line 52 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ TP

| etiss_uint64 RV64IMACFD::TP |

Definition at line 25 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ X

| etiss_uint64 * RV64IMACFD::X |

Definition at line 53 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

◆ ZERO

| etiss_uint64 RV64IMACFD::ZERO |

Definition at line 21 of file RV64IMACFD.h.

Referenced by RV64IMACFDArch::resetCPU().

The documentation for this struct was generated from the following files:

- include/jit/Arch/RV64IMACFD/RV64IMACFD.h

- /home/runner/work/etiss/etiss/ArchImpl/RV64IMACFD/RV64IMACFD.h