connects a wishbone bus interface implemented with the variables of WishboneSignalMap to a ETISS_System structure. More...

#include <Wishbone.h>

Public Member Functions | |

| WishboneBus (WishboneSignalMap< BOOLSIG, VECTORSIG > &sigs, ETISS_System &system, ETISS_CPU &cpu, etiss::CPUCore &core) | |

| Constructor. | |

| void | init () |

| Initiate all bus output signals and set pending status to "nothing pending". | |

| etiss_int32 | update (uint64_t time, bool premain, bool reset, bool posSimTime=true) |

| Update signals to CPU or read/write from/to bus. | |

Public Member Functions inherited from etiss::interfaces::Delegate Public Member Functions inherited from etiss::interfaces::Delegate | |

| Delegate (ETISS_System &system, ETISS_CPU &cpu) | |

| void | syncTime (uint64_t time_ps) |

| etiss::int32 | read (bool ibus, uint64_t &time_ps, uint64_t addr, uint8_t *buf, unsigned len) |

| handles read operations. | |

| etiss::int32 | write (bool ibus, uint64_t &time_ps, uint64_t addr, uint8_t *buf, unsigned len) |

| handles write operations. | |

Public Attributes | |

| WishboneSignalMap< BOOLSIG, VECTORSIG > & | sigs |

| Signals between bus and CPU. | |

Public Attributes inherited from etiss::interfaces::Delegate Public Attributes inherited from etiss::interfaces::Delegate | |

| std::function< etiss::int32(bool, uint64_t &, uint64_t, uint8_t *, unsigned, bool &, bool &)> | injectedRead |

| if valid then this function will be called by read() instead of performing any action itself | |

| std::function< etiss::int32(bool, uint64_t &, uint64_t, uint8_t *, unsigned, bool &, bool &)> | redirectedWrite |

| std::function< void(bool injected, const uint64_t &time_ps, uint64_t addr, const uint8_t *buf, unsigned len)> | snoopRead |

Private Member Functions | |

| void | flipEndianness (uint8_t *buf) |

| Flips endianess of a VECTORSIG. | |

| bool | sel2Length (uint32_t sel, unsigned &length, unsigned &addressOffset) |

| Calculates length and offset out of signal sel. | |

Private Attributes | |

| etiss::CPUCore & | core_ |

| uint64_t | lastutime |

| time of last signal evaluation phase | |

| uint64_t | etime |

| bool | lastclock |

| used for determining clock edge | |

| bool | useposclkedge |

| use positive or negative clock edge | |

| VECTORSIGSTORAGETYPE | dat_o |

| buffer for data out to CPU | |

| bool | po_err |

| bus error arised | |

| unsigned | pending |

| 0: nothing pending; 1: Read pending; 2: Write pending | |

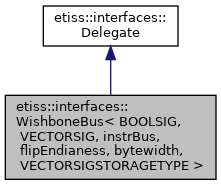

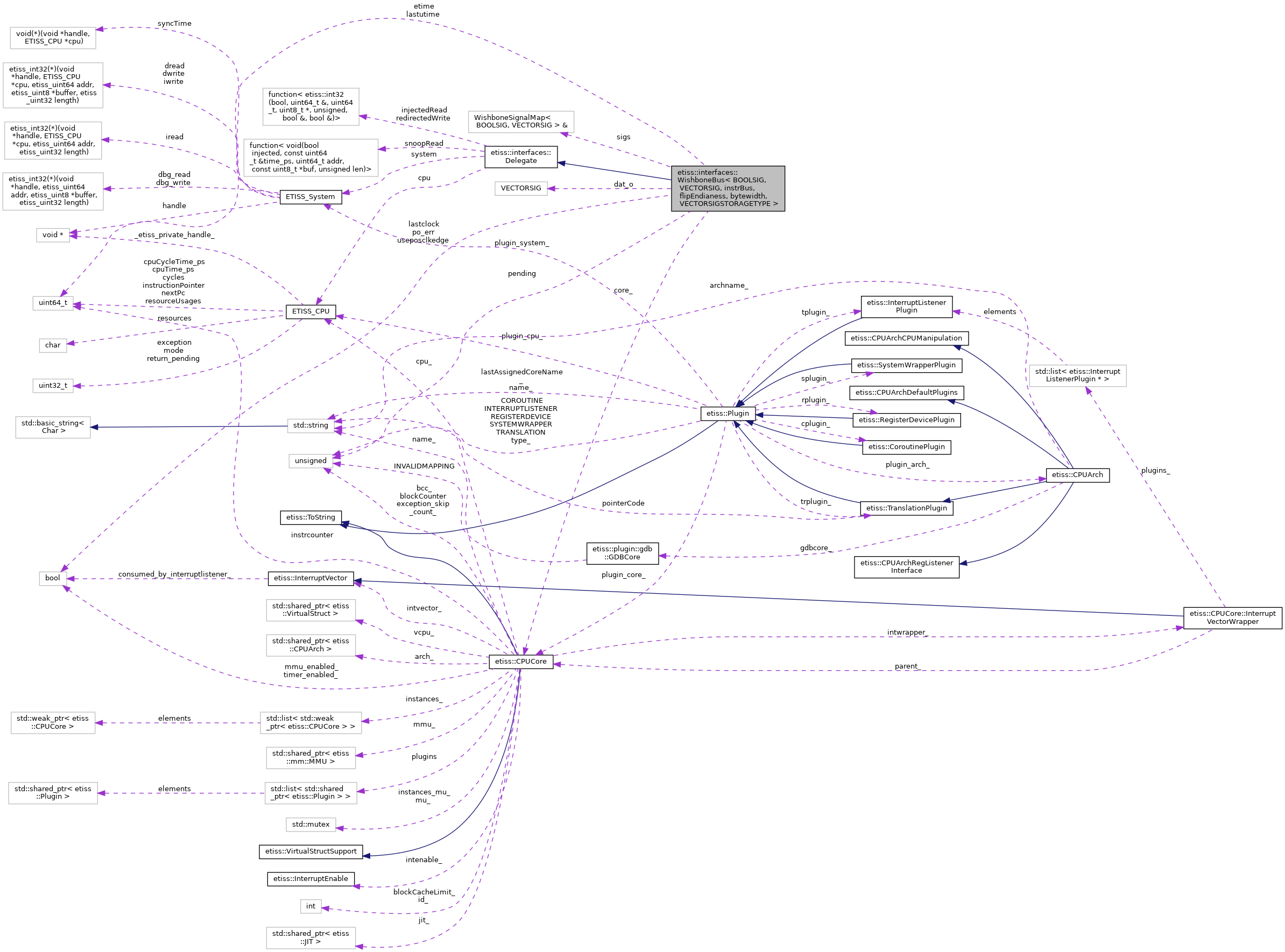

Detailed Description

class etiss::interfaces::WishboneBus< BOOLSIG, VECTORSIG, instrBus, flipEndianess, bytewidth, VECTORSIGSTORAGETYPE >

connects a wishbone bus interface implemented with the variables of WishboneSignalMap to a ETISS_System structure.

the template parameter instrBus defined is the iread/iwrite or dread/dwrite functions are used (-> instruction bus or data bus)

Definition at line 140 of file Wishbone.h.

Constructor & Destructor Documentation

◆ WishboneBus()

|

inline |

Constructor.

- Parameters

-

sigs Signals between bus and CPU system Underlying ETISS system for accessing external bus cpu ETISS CPU state

Definition at line 151 of file Wishbone.h.

Member Function Documentation

◆ flipEndianness()

|

inlineprivate |

Flips endianess of a VECTORSIG.

Definition at line 332 of file Wishbone.h.

◆ init()

|

inline |

Initiate all bus output signals and set pending status to "nothing pending".

Definition at line 166 of file Wishbone.h.

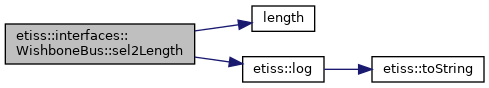

◆ sel2Length()

|

inlineprivate |

Calculates length and offset out of signal sel.

- Parameters

-

[in] sel Select signal [out] length Number of Bytes to read/write [in] addressOffset Offset on the aligned address (is proved in this function)

- Returns

- Select signal was valid

Definition at line 350 of file Wishbone.h.

References length(), etiss::log(), and etiss::WARNING.

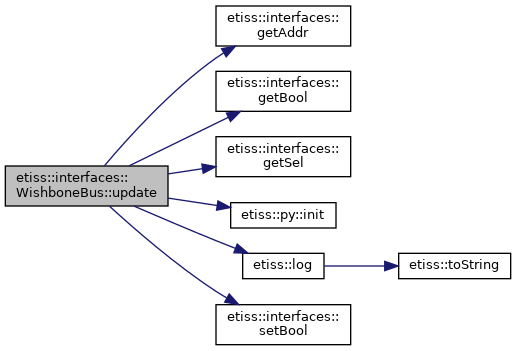

◆ update()

|

inline |

Update signals to CPU or read/write from/to bus.

Has to different tasks depending on parameter premain: In the premain phase all signals are updated on the CPU side. Otherwise the signals are evaluated for bus access and a read or write access can be fulfilled.

- Parameters

-

time Actual simulation time premain Determines premain phase reset Determines if CPU sends reset signal posSimTime If true, time is checked if it has elapsed

Definition at line 185 of file Wishbone.h.

References bool, etiss::ERROR, etiss_log, etiss::FATALERROR, etiss::interfaces::getAddr(), etiss::interfaces::getBool(), etiss::interfaces::getSel(), etiss::log(), etiss::interfaces::setBool(), uint64_t, and uint8_t.

Member Data Documentation

◆ core_

|

private |

Definition at line 402 of file Wishbone.h.

◆ dat_o

|

private |

buffer for data out to CPU

Definition at line 407 of file Wishbone.h.

◆ etime

|

private |

Definition at line 404 of file Wishbone.h.

◆ lastclock

|

private |

used for determining clock edge

Definition at line 405 of file Wishbone.h.

◆ lastutime

|

private |

time of last signal evaluation phase

Definition at line 403 of file Wishbone.h.

◆ pending

|

private |

0: nothing pending; 1: Read pending; 2: Write pending

Definition at line 409 of file Wishbone.h.

◆ po_err

|

private |

bus error arised

Definition at line 408 of file Wishbone.h.

◆ sigs

| WishboneSignalMap<BOOLSIG, VECTORSIG>& etiss::interfaces::WishboneBus< BOOLSIG, VECTORSIG, instrBus, flipEndianess, bytewidth, VECTORSIGSTORAGETYPE >::sigs |

Signals between bus and CPU.

Definition at line 399 of file Wishbone.h.

◆ useposclkedge

|

private |

use positive or negative clock edge

Definition at line 406 of file Wishbone.h.

The documentation for this class was generated from the following file:

- /home/runner/work/etiss/etiss/include/etiss/interfaces/Wishbone.h