defines main cpu core interface More...

#include "etiss/Misc.h"#include "etiss/InterruptVector.h"#include "etiss/VirtualStruct.h"#include <mutex>#include <memory>#include <list>

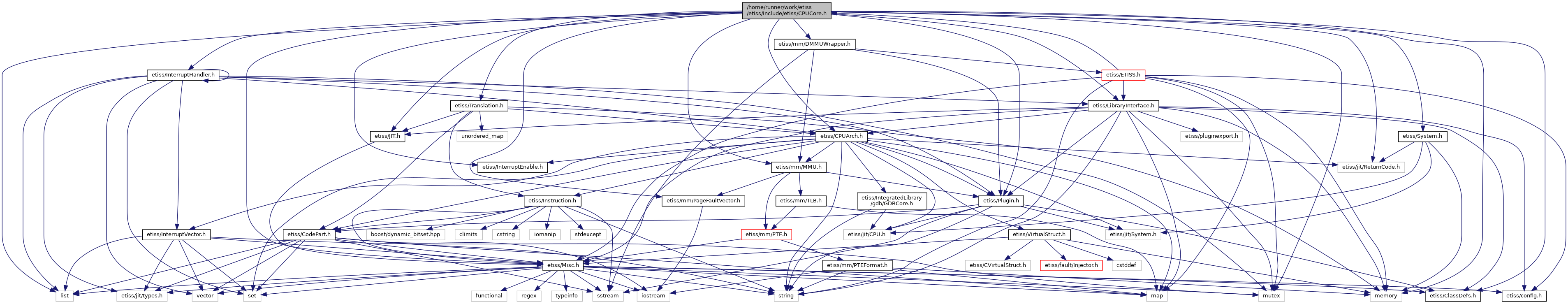

Include dependency graph for CPUCore.h:

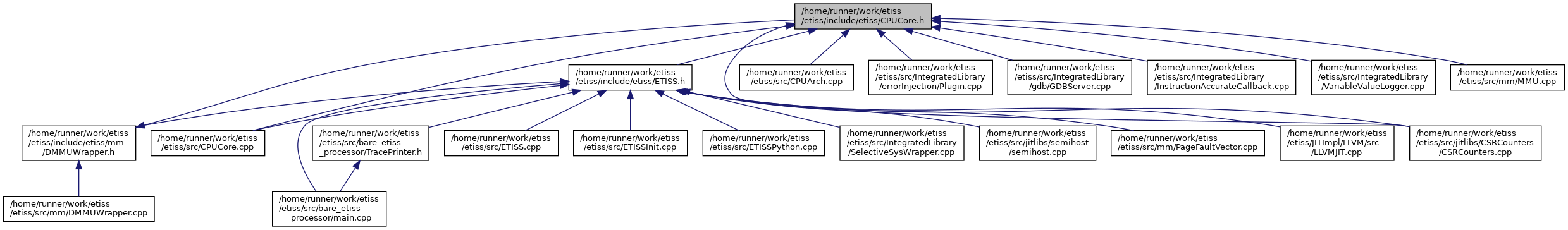

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| class | etiss::CPUCore |

| CPUCore is responsible for the simulation of a CPU core in ETISS. More... | |

| class | etiss::CPUCore::InterruptVectorWrapper |

Namespaces | |

| namespace | etiss |

| forwards: include/jit/* | |

Macros | |

| #define | ETISS_CPUCORE_DBG_APPROXIMATE_INSTRUCTION_COUNTER 0 |

Detailed Description

defines main cpu core interface

Definition in file CPUCore.h.