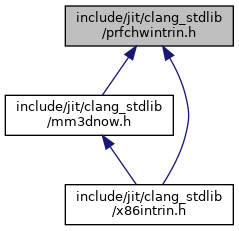

Go to the source code of this file.

Functions | |

| static __inline__ void | __attribute__ ((__always_inline__, __nodebug__)) _m_prefetch(void *__P) |

| Loads a memory sequence containing the specified memory address into all data cache levels. | |

Function Documentation

◆ __attribute__()

|

static |

Loads a memory sequence containing the specified memory address into all data cache levels.

Loads a memory sequence containing the specified memory address into the L1 data cache and sets the cache-coherency to modified.

The cache-coherency state is set to exclusive. Data can be read from and written to the cache line without additional delay.

This intrinsic corresponds to the PREFETCHT0 instruction.

- Parameters

-

__P A pointer specifying the memory address to be prefetched.

This provides a hint to the processor that the cache line will be modified. It is intended for use when the cache line will be written to shortly after the prefetch is performed.

Note that the effect of this intrinsic is dependent on the processor implementation.

This intrinsic corresponds to the PREFETCHW instruction.

- Parameters

-

__P A pointer specifying the memory address to be prefetched.

Definition at line 28 of file prfchwintrin.h.